Chip Services

Chip Services

Products

Products

- Automotive and Industrial control

- Information Security

- Edge Computing& Network Communication

Products

Resources

Resources

Language

Language

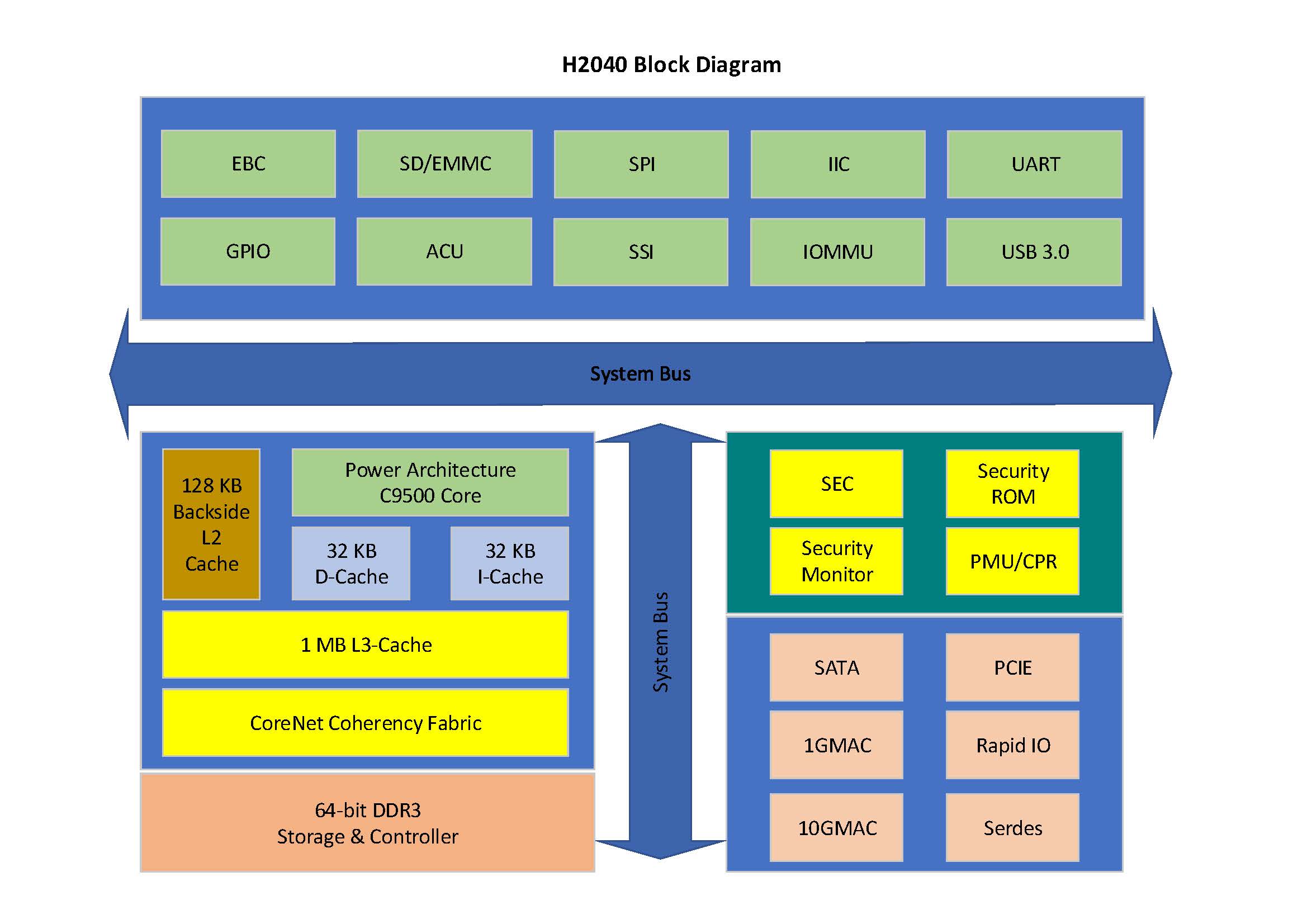

The H2040 chip is a high-performance edge computing chip equipped with a quad-core microprocessor of C9500, operating at a maximum frequency of 1.3GHz. C9500 is a PowerPC processor core with dual-issue, 7-stage pipeline, and superscalar . H2040 integrates various peripherals on the chip, such as PCI-E 3.0, USB3.0 OTG, RapidIO2.2, 10G Ethernet, and 1G Ethernet.

H2040 supports both national and international cryptographic algorithms, including national standards cryptographic of SM2/SM3/SM4/SM9 and international standards cryptographic of RSA, AES, DES, SHA0, SHA1, SHA224, SHA256, and other recognized algorithms.

? Compatible with NXP e500MC core

? Native support for multiprocessor systems

? 32KB instruction CACHE, 32KB data CACHE

? 128KB L2 CACHE

? MMU support

? 1MB L3 Cache

? Supporting public key cryptographic algorithms and symmetric cryptographic algorithms

? Supporting national cipher algorithm of SM2/SM3/SM4/SM9

? Supporting international algorithms of RSA/AES/DES/SHA

? Supporting reconstructed algorithms

? Temperature detection

? Voltage detection

? Frequency detection

? True random number generator with maximum output data rate of 20M

? Supporting 64-bit data + 8-bit for ECC data

? Supporting 8-bit and 16-bit data width

? Supporting up to 800MHz, 1.6GT/s

? Compatible with PCI-E 3.0

? Supporting X4 connection, can be used in RC or EP mode

? Compatible with RapidIO 2.2 and backward compatible with RapidIO 2.1/2.0/1.3/1.2/1.1

? Supporting DMA operation

? Supporting USB3.0 high-speed standard and OTG function

? Supporting point-to-point transfer with a high-speed, full-speed, or low-speed USB device

? Supporting Session Request Protocol (SRP) and Host Negotiation Protocol (HNP)

? Supporting Suspend and Resume low power control

? Supporting DMA access to FIFO

? Supporting 10G-BASE-KR mode, compatible with 10G-BASE-R through parallel detection

? 10G-BASE-KR mode supports FEC error correction

? Supporting 4-CH sending and receiving engine

? 16KB Rx FIFO and 16KB Tx FIFO

? Supporting 2 10GE Ethernet interfaces

? Supporting 10/100/1000Mbps half-duplex or full-duplex Ethernet access

? Used in various Ethernet application scenarios

? Power management

? Different packet processing characteristics

? Supporting 8 1GE Ethernet interfaces

? Complied with SATA3.0 standard, backward compatible with SATA 1.0 and 2.0

? Supporting 4 channels

? Supporting high-speed DMA based on descriptors

? Supporting 8 ROM, EPROM, SRAM, Flash or peripheral chip selection

? Supporting Burst and non-Burst transmission

? Supporting 8-bit and 16-bit

? Programmable access time for each device

? Supporting serial master mode operation

? Supporting DMA controller interface

? Supporting enhanced SPI

? Supporting SD3.0 and 3.01 specifications, including eSD

? Supporting SDIO 3.0, including eSDIO

? Optional 16 or 64-byte FIFOs for sending or receiving data

? Programmable baud rate, data bits, parity check, and stop bits

? Supporting DMA access

? Compatible with Philips Semiconductor I2C standard

? 2 independent 4*1byte data buffers

? Detecting illegal start and stop signals

? Power domain: 0.9V, 1.0V, 1.5V, 1.8V, 3.3V

? Packaging: CBGA1295

? Supporting master/slave mode operation

? SPI operation can be controlled in Doze mode

? Programmable data frame size from 4-16bits

? Supporting time calibration in high-speed transmission mode

? Complete development environment

? Rich driver library

? Complete application solution