Chip Services

Chip Services

Products

Products

- Automotive and Industrial control

- Information Security

- Edge Computing& Network Communication

Products

Resources

Resources

Language

Language

Overview:

CUni360S-Z is an information security chip applicable to contact IC and magnetic strip cards It is designed based on the 32-bit security CPU CS0 with independent intellectual property rights. CUni360S-Z is distinguished by low power consumption, high performance, multifunction and high security level. It can be widely used in POS machines, dual-interface card readers, dynamic QR code terminals, and other fields. The chip’s typical operating frequency is 60MHz.

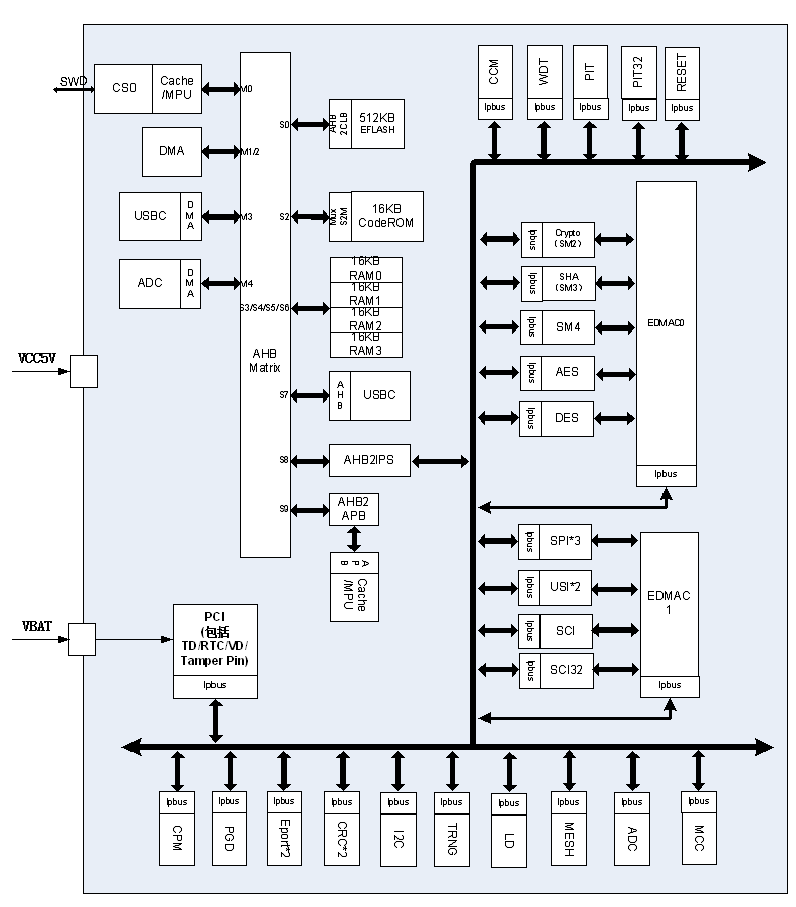

Block diagram of CUni360S-Z

Package Type

| Pin | Package type and pin assignment(mm) | |

QFN40(5*5) | QFN76(9*9) | |

SPI(multiplexed) | 2 | 3 |

I2C | 1 | 1 |

SSI | 2 | 1 |

SCI | 2 | 2 |

ISO7816 | 0 | 2 |

USB | 1 | 1 |

ADC(multiplexed) | 0 | 3 |

PWM(multiplexed) | 3 | 4 |

MCC | 0 | 1 |

EPORT(multiplexed) | 6 | 16 |

SDIO(tamper-resistant) | 4 | 8 |

? 64K bytes of SRAM

? 16K bytes of ROM

? 512K bytes of EFLASH. 512 bytes/Page, minimum 100,000 erase cycles

? 32-bit low-power RISC core with highly optimized 3-stage pipeline

? Supporting byte, half-word, and word memory access

? Supporting interrupt nesting

? Supporting single-cycle 32-bit x 32-bit hardware integer multiplier array, 3 to13 cycle hardware integer frequency divider array

? Memory protection unit (MPU)

? Low power consumption and high performance

? Supporting Cache

? Timing module EPT

? DMA/EDMA

? 2 timers(PIT)

? Watchdog(WDT)

? Real-time clock(RTC)

? Time counter(TC)

? 1024bit RSA@60MHz

? 2048bit RSA@60MHz

? 256bit SM2 prime field @60MHz

? DES/3DES supports ECB/CBC mode

? AES supports ECB/CBC/CTR mode

? SM4 supports ECB/CBC mode

? SM3

? SHA-0/ SHA-1/ SHA-224/ SHA-256/ SHA-384/ SHA-512

? Supporting CRC32/ CRC16/ CRC8

? Supporting DMAC operation

? Application-oriented memory partitioning with hardware support for secure isolation

? Scrambling bus

? True random number generator, compliant with FIPS 140-2 standards and national commercial cryptographystandards

? Voltage detection unit

? Light detection unit

? Power supply burr detection unit

? Metal shielding protection

? Temperature detection unit

? Frequency detection unit

? Clock and reset pulse filtering

? Optimizing wire routing for security

? Supporting 128 Byte NVSRAM

? Supporting 4 pairs of decapsulation signals, configured with dynamic/static detection mode

? Supporting voltage detection

? Supporting temperature detection

? Supporting self-destruct and clear NVSRAM

? Unique serial number for each product

? Main power input voltage: 2.5V~5.5V, PCI field input voltage: 1.9V~3.62V

? ypical power consumption: 20mA @ 60MHz

? Low-power sleep mode: less than 50uA

? ESD (HBM): 2500V

? Supporting internal power-on reset and external reset

? Level II of security chip for commercial crypto product certification

? EAL4+ of China Cybersecurity Review Technology and Certification Center

? Terminal Chip Security Assessment (compliant with PCI 5.1)

? Dual-interface card reader

? POS

? Personal payment terminal

? ID card reader

? Dynamic QR code terminal

? Complete development environment

? Rich driver libraries

? Complete application solutions